# **EICASLAB**<sup>TM</sup> DEMO

The Professional Software Suite for Automatic Control Design and Forecasting

EICASLAB Demo RT-emb

Beagle Bone at work!

Part 5: TARGET

Hardware-in-the-loop

# **Target**

The Target operative mode allows to export the control algorithm to the final hardware target that will execute it to control first the simulated plant in Hardware-in-the-loop and then the real plant in Final Validation Test sub-modes.

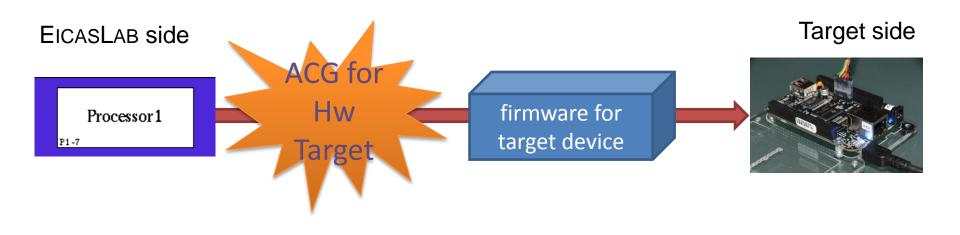

# Target: ACG for HW Target

## **Target**

EICASLAB provides the routines to generate the *Basic Software*, not only for the EICASLAB RCP Platform itself, but also for a family of devices or for a specific hardware architecture.

#### ACG means Automatic Code Generation

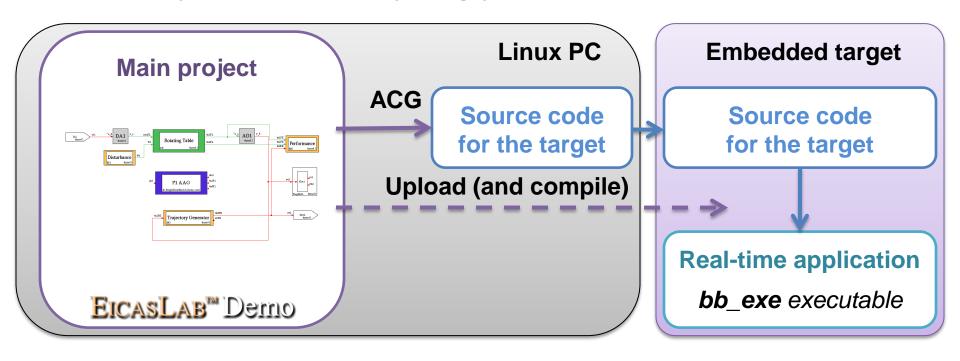

# Target: ACG, compile & upload

# **Target**

The EICASLAB Target Module for Beagle Bone enables

- The code generation for the Beagle Bone target

- The upload and compiling process

# Hardware-in-the-loop (HIL)

# Hardware-in-the-loop

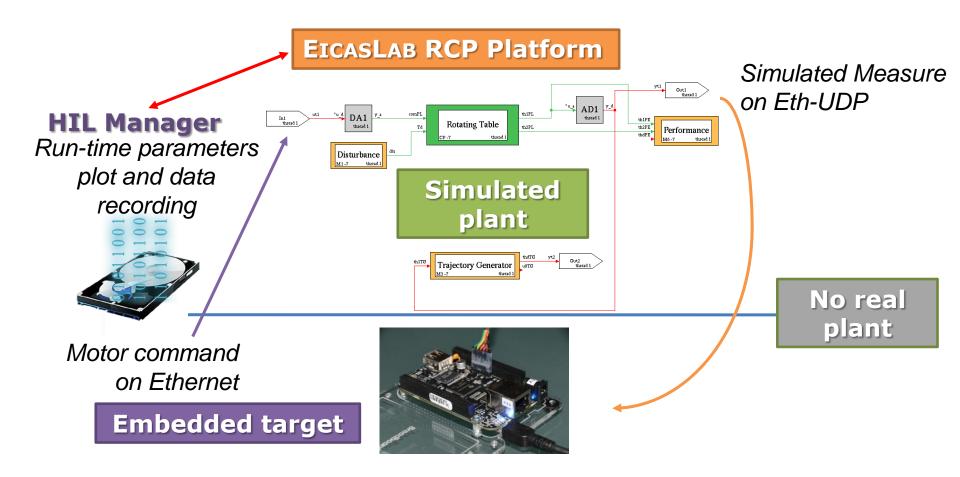

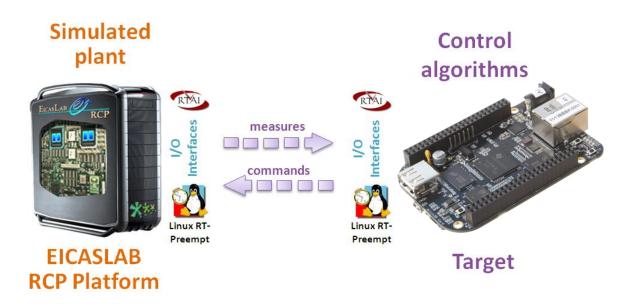

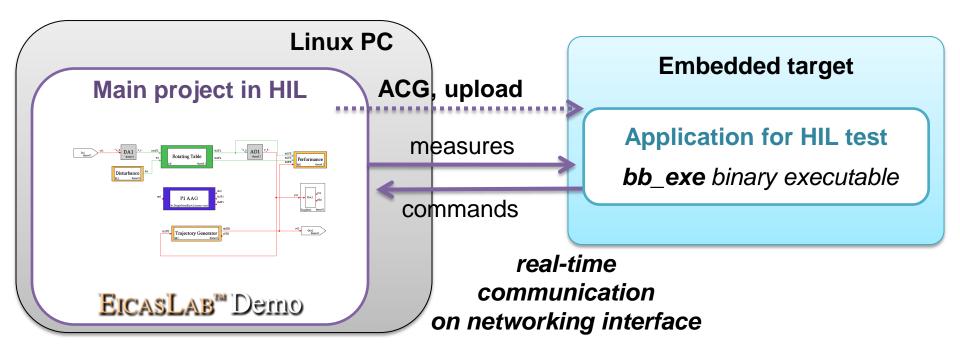

The Hardware-in-the-loop operative sub-mode allows to test the control algorithms running on the final hardware target suitably connected with the EICASLAB RCP Platform, in which the simulated plant is executed.

# HIL: the system layout

# Hardware-in-the-loop

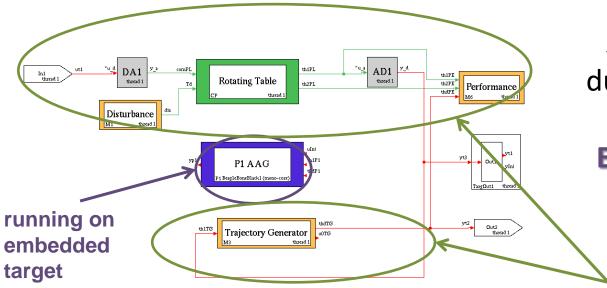

The **system layout** in HIL sub-mode:

The system layout shows that the *Plant Area* is enabled again: during the HIL trials it is simulated by the **EICASLAB RCP Platform**.

real-time simulated

Who does what in Hardware-in-the-loop operative submode in RT-emb demo:

| HW | EICASLAB<br>RCP Platform | Embedded board target | Rotating Table emulator |

|----|--------------------------|-----------------------|-------------------------|

| SW | simulates plant          | runs control<br>logic | unused                  |

When the demo is in HIL operative sub-mode the "**ACG for HIL**" advanced feature generates the BS + AS for performing the Hardware-in-the-loop

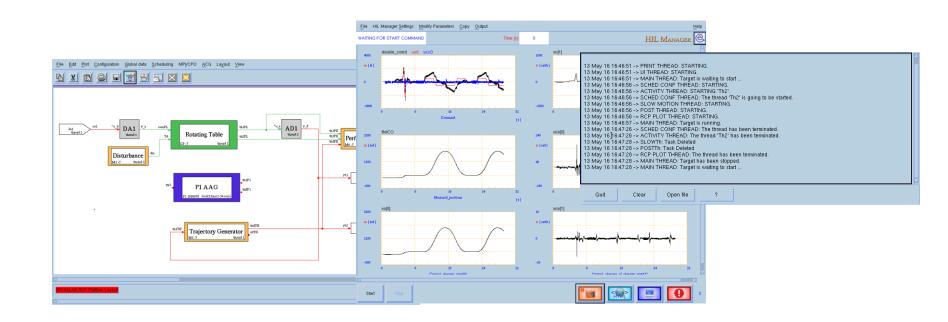

The **HIL Manager** tool manages the overall Hardware-in-the-loop trial.