excellence and passion in automatic control design

# Activity scheduling in $EICASLAB^{TM}$

Welcome to Innovation

Via Vincenzo Vela, 27 10128 Torino - ITALY (IT) Tel. +39 011 56 23 798 +39 011 56 23 088 Fax +39 011 43 60 679

excellence and passion in automatic control design

# TABLE OF CONTENT

- Activity scheduling as professional support to design control hardware & software architecture

- Scheduling in the Simulation phase

• Scheduling in the Rapid Control Prototyping phase

excellence and passion in automatic control design

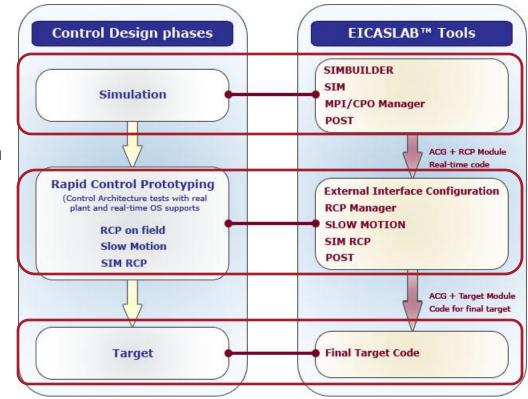

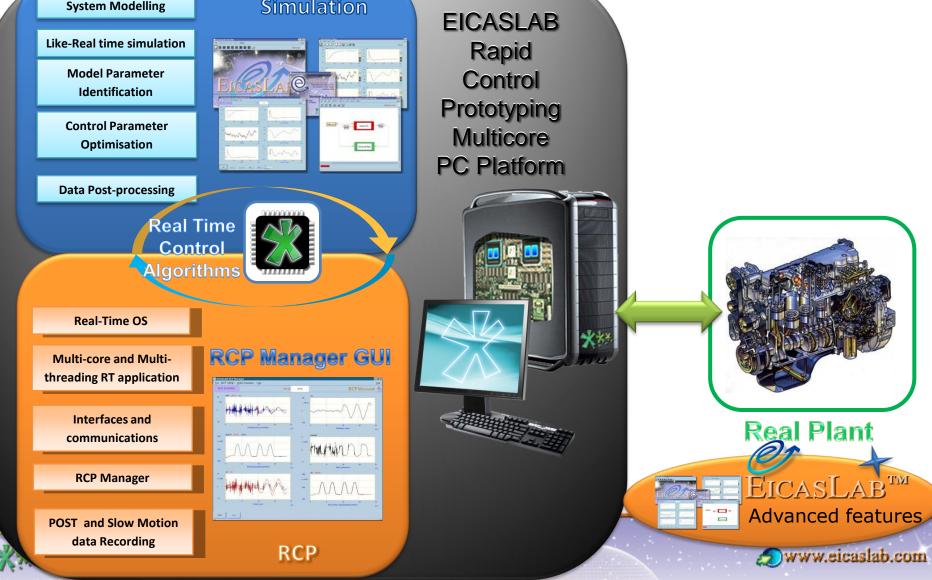

# $EICASLAB^{TM}$ assists you in all the control design phases

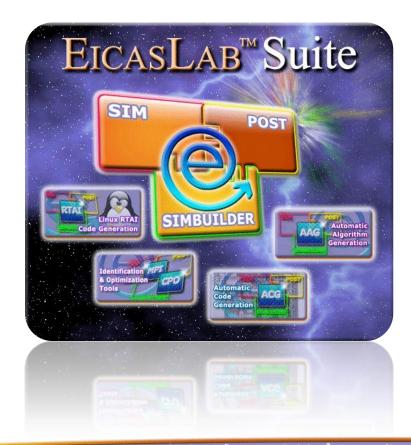

EICASLAB is the professional software suite that supports you in all the control design phases: from the system concept to the code generation for the final target.

Specifically, EICASLAB provides a professional support and specific tools devoted to the following control design phases:

#### Simulation

Rapid Control Prototyping (RCP)

Code generation for the final target

excellence and passion in automatic control design

# **EICASLAB**<sup>™</sup> takes particular care of the control software & hardware architecture

EICASLAB allows you to develop hardware architectures including multiprocessors and software architectures including multi-level hierarchical control function.

A support is given for allocating each control activity to a given processor.

The scheduling of all the activities involved in a control system is a key task for the successful development of the control system itself.

EICASLAB provides a fundamental and professional support for a correct scheduling of your system in all the control design phases.

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

In the Simulation phase three different working areas are available:

**MISSION AREA**

CONTROL

MISSION

Automatic

control

PLANT

MISSION

u(i)

disturbances

PLANT

**PLANT AREA**

y(i)

- the Control Area,

- the Plant Area,

- the Mission Area.

The designer must schedule all the activities of these 3 areas.

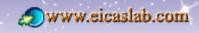

Each activity is composed by:

Asynchronous

commands from host

Trajectory

generation

r,(i)

CONTROL AREA

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

# The activities scheduling

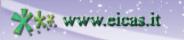

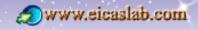

The designer must fix a simulation step,

which represents the time resolution applied in the simulation of your overall project.

The periodic functions are characterized by the following scheduling parameters (expressed as a multiple of the simulation step):

- Phase time at which they are called for the first time,

- **Period** their sample time interval,

To guarantee the correct scheduling of the activity it is necessary to take into account its duration

Two periodic functions are available:

| execution function | It executes all the operations that the activity must perform each time it is scheduled | It is called when the activity is scheduled (considering its phase and its period) |

|--------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| output function    | It computes and updates the outputs of the activity as a function of its current state  | It is called after the fixed duration                                              |

www.eicas.it

excellence and passion in automatic control design

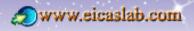

#### The Scheduling in the Simulation phase

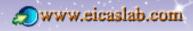

# The Activities schedule window

All the activities are listed in the following order:

- Plant Area activities,

- the Converters activities,

- Mission Area activities,

- Control Area activities.

The 'Active' push enables or disables the corresponding activity.

The **Period**, **Duration** and **Phase** of each activity can be set.

EICASLAB supports you and prevents you to make scheduling errors.

excellence and passion in automatic control design

Block

#### The Scheduling in the Simulation phase

# The EICASLAB scheduler of the SIM tool

The SIM tool manages the scheduling of activities by means of the **EICASLAB scheduler**, H an advanced engine that allows to run like real-time simulations

The EICASLAB scheduler is the core of the time scheduling algorithms.

On the basis of the constraints fixed in the 'Activities Scheduling' window.

It defines the order in which the functions of a given activity have to be executed

It schedules the data trasmission among all the activities

The EICASLAB scheduler is directly linked to the clock of the CPU: if the simulation is fast enough it may allow to run a real-time simulation.

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

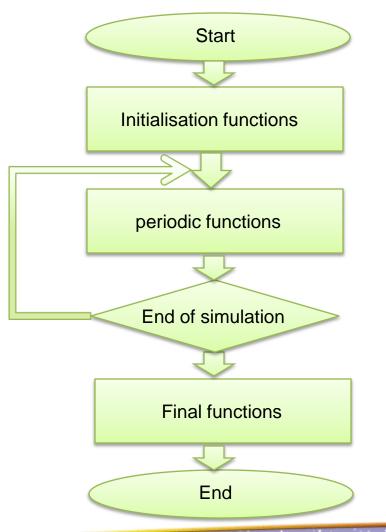

# The EICASLAB scheduler simulations

w.eicas.it

The EICASLAB scheduler performs a simulation with period equal to the simulation step.

Intialization functions

Project parameters reading

Project initial state reading

User initialisation functions

Periodic functions

Output functions (Updating of the outputs)

Signal Propagation

Plot update (SIM plotting and POST file recording)

Execution functions

Time update

Final functions

User final functions

Project final state saving

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

# **Initialisation functions**

The schedulable activities have a set of 'initial functions' called just once at the beginning of the simulation.

| Function<br>description      | Activities concerned                          | Order of scheduling |

|------------------------------|-----------------------------------------------|---------------------|

| Parameter file reading       | All activities that have parameters           |                     |

| Resolution file reading      | Only Continuous Plant                         |                     |

| Initial state file reading   | All activities that have state variables      |                     |

| Control design               | Only the control functions                    |                     |

| User initialisation function | Only activities programmed in ANSI C language |                     |

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

#### **Final functions**

The schedulable activities have a set of 'final functions' called just once at the end of the simulation.

| Function<br>description  | Activities concerned                          | Order of scheduling |

|--------------------------|-----------------------------------------------|---------------------|

| User final function      | Only activities programmed in ANSI C language |                     |

| Final state file writing | All activities that have state variables      |                     |

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

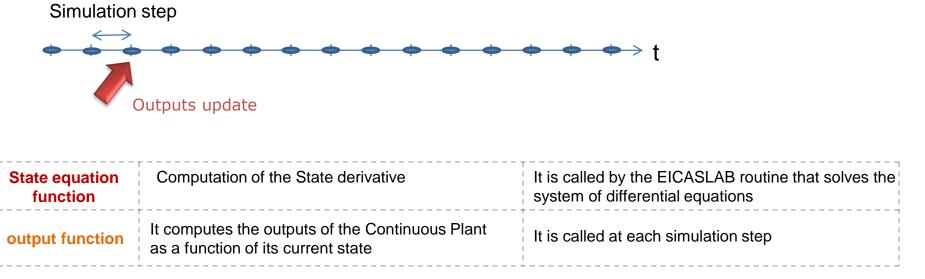

# **Continuous Plant scheduling**

The Continuous Plant is the mathematical fine model of the plant to be controlled. It is a dynamic system - with state and outputs variables - that can be represented through a system of differential equations.

The integration of such a system is performed through a smart integration procedure embedded in EICASLAB.

The outputs of the Continuous Plant are updated at each simulation step.

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

# **Instantaneous activities scheduling**

The duration of some activities is null or negligible with respect to the duration of the other ones: they are called instantaneous.

Their scheduling is then defined just by the **Phase** and **period**.

#### Instantaneous activities

**Experimental Data**

**Elementary missions**

A/D and D/A Converters

Processor Input/Output

#### Instantaneous activities periodic functions

| execution function | perform each time it is scheduled and | called when the block is scheduled (considering its phase and its period) |

|--------------------|---------------------------------------|---------------------------------------------------------------------------|

|                    | updates its outputs                   |                                                                           |

excellence and passion in automatic control design

#### The Scheduling in the Simulation phase

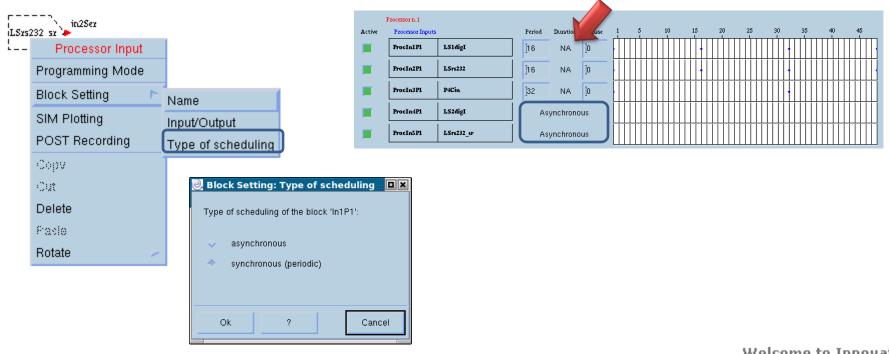

# **Processor Inputs: Synchronous and asynchronous activities**

The processor inputs represent the interrupt activities that receive and process the inputs coming in your processor.

Such inputs can be received:

with a given periodicity (synchronous processor inputs),

through an asyncrounous communication (asynchronous processor inputs).

excellence and passion in automatic control design

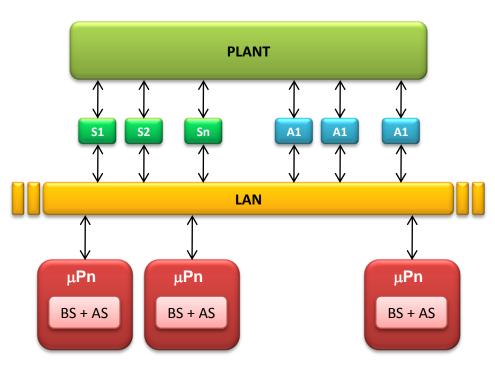

#### The scheduling in the Rapid Control Prototyping phase

The Rapid Control Prototyping phase allows you to test and validate your control software by transferring it in a smart PC Platform equipped with a suitable RTOS and by directly piloting your plant, before the transfer in the final target.

The Rapid Control Prototyping phase is fundamental for minimizing time and costs in the control tuning in field.

# EXAMPLE Elected and passion in automatic control design Excellence and passion in automatic

excellence and passion in automatic control design

#### The scheduling in the Rapid Control Prototyping phase

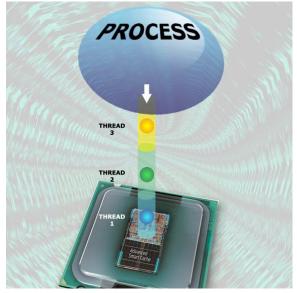

# **Multi-core & multi-thread applications**

A **multi-core processor** is a processing system composed by two or more independent cores. While in single core CPU systems, it is not possible to execute more than one piece of code at a same time, in a multi-core processor each core can run a portion of code so that a real concurrent execution is achieved.

A **thread** is a unit of executable code. In a thread-based multitasking environment all processes have at least one thread of execution, which is called the main thread. Each multithreaded process starts with the main thread that creates one or more additional child threads.

**Multithreading** changes the fundamental architecture of a program. Unlike a single-threaded program that executes in a strictly linear way, a multithreaded program executes portions of itself concurrently. Then a single program can perform two or more tasks concurrently. The true concurrent execution is possible only in a multiple-CPU or multi-core CPU systems.

excellence and passion in automatic control design

#### The scheduling in the Rapid Control Prototyping phase

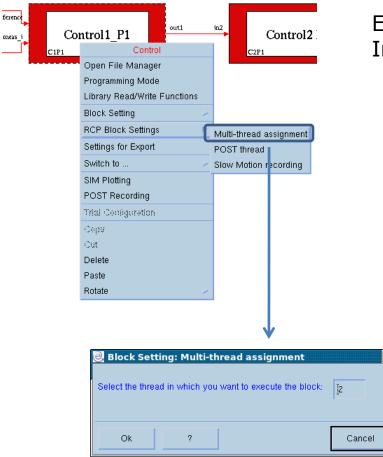

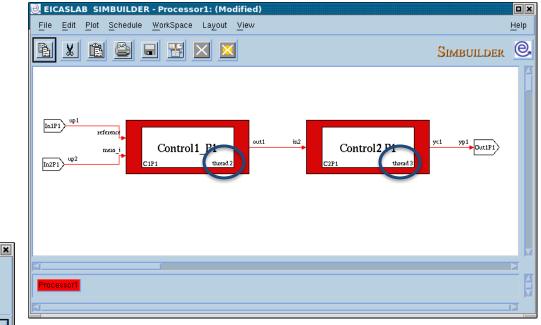

# **Scheduling, cores & threads**

The Control system works directly with the real Plant, then just the Control Area must be scheduled.

To guarantee the correct emulation of the Target control architecture, in the **Rapid Control Prototyping** phase, the user could have the need of reviewing the control scheduling.

The new scheduling requires to organize the control functions in **threads**, that will be distributed on the **cores** of the multi-core CPU available in the PC platform, thanks to the application in EICASLAB of multithreading and multi-core programming techniques.

| Providence and     |            |

|--------------------|------------|

|                    | Complexes  |

| Mass.              | erol3 P1   |

|                    |            |

|                    |            |

|                    |            |

| MULTI-CORE & MULTI |            |

| HOLIT-COKE & HOLIT | -THREADING |

|                    |            |

|                    |            |

|                    |            |

There is no more simulation step: instead of it the clock tick of the real-time operative system is considered.

# excellence and passion in automatic control design The scheduling in the Rapid Control Prototyping phase

# Thread of the activities

Every Control function and Processor Input/Output has to be associated to a thread.

ww.eicas.it

#### **EICAS** Automazione S.p.A.

excellence and passion in automatic control design

#### The scheduling in the Rapid Control Prototyping phase

#### **Core & thread setting**

| Calif. Diet. Calessinia                                            | MDRCDO Levent Marrie              |                     |                                                                                                                     | Links           |                                           |

|--------------------------------------------------------------------|-----------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------|

|                                                                    | MPI/CPO Layout View               |                     |                                                                                                                     | Help            | Core manage                               |

| ative Modes <u>C</u> onfigurat                                     | tion <u>A</u> CG                  |                     |                                                                                                                     |                 | 2 core manage                             |

| an field anthings b                                                |                                   |                     | SIMP                                                                                                                | UILDER 🔍 T      | Thread and core ma                        |

|                                                                    | ating system selection            |                     | 1911vil                                                                                                             |                 | rificad and core in                       |

|                                                                    | management                        | J                   |                                                                                                                     | fi              | 🗇 default                                 |

|                                                                    | R: /home/webinar/MyProje          | ct.elp - System Lay | yout                                                                                                                |                 | custom                                    |

| Edit Plot Schedule                                                 | MPI/CPO Layout View               |                     |                                                                                                                     | Help            | - Cuctom                                  |

| ative Modes <u>C</u> onfigurati                                    | ion <u>A</u> CG                   |                     |                                                                                                                     |                 |                                           |

|                                                                    |                                   |                     | SIMB                                                                                                                | UILDER 🔍 –      |                                           |

|                                                                    | ting system selection             |                     |                                                                                                                     |                 | 01                                        |

|                                                                    | management<br>d configuration     |                     |                                                                                                                     |                 | Ok                                        |

|                                                                    | path configuration                | ,                   |                                                                                                                     |                 |                                           |

|                                                                    | Aanager parameter definition      |                     |                                                                                                                     |                 |                                           |

| Data 5                                                             | De seudin a                       |                     |                                                                                                                     |                 |                                           |

| Data P                                                             | Recording 😕                       |                     |                                                                                                                     |                 |                                           |

| Data F                                                             | Recording                         |                     |                                                                                                                     |                 |                                           |

|                                                                    |                                   |                     |                                                                                                                     |                 |                                           |

|                                                                    | Command                           |                     |                                                                                                                     |                 |                                           |

|                                                                    | Command                           |                     |                                                                                                                     |                 |                                           |

|                                                                    | Command                           | Priority            | Hard/soft real time                                                                                                 | Schedule policy | Stack dimensi                             |

| Tread configura                                                    | Command<br>tion<br>Assigned core  |                     |                                                                                                                     |                 |                                           |

| Thread n.1                                                         | Command<br>Ition<br>Assigned core | Į                   |                                                                                                                     | Schedule policy | <u>]</u> 1024                             |

| Thread                                                             | Command<br>tion<br>Assigned core  |                     |                                                                                                                     |                 |                                           |

| Thread n.1                                                         | Command<br>Ition<br>Assigned core | h<br>h              | <ul> <li>A hard ↓ soft</li> <li>A hard ↓ soft</li> </ul>                                                            | FIFO -          | jĭ1024<br>jĭ1024                          |

| Thread n.1<br>Thread n.1<br>Thread n.4<br>Thread n.5               | Command<br>Ition<br>Assigned core | Į                   | <ul> <li>A hard ↓ soft</li> <li>A hard ↓ soft</li> </ul>                                                            | FIFO -          | <u>]</u> 1024                             |

| Thread n.1<br>Thread n.1                                           | Command<br>Ition<br>Assigned core | h<br>h              | <ul> <li>A hard ↓ soft</li> <li>A hard ↓ soft</li> </ul>                                                            | FIFO -          | jĭ1024<br>jĭ1024                          |

| Thread n.1<br>Thread n.1<br>Thread n.4<br>Thread n.5               | Command<br>tion<br>Assigned core  | ji<br>ji<br>ji      | <ul> <li>hard v soft</li> </ul> | FIFO            | j1024<br>j1024<br>j1024<br>j1024<br>j1024 |

| Thread n.1<br>Thread n.1<br>Thread n.4<br>Thread n.5<br>Thread n.6 | Assigned core                     | Ĭ1<br>Ĭ1<br>Ĭ1      | <ul> <li>hard v soft</li> <li>hard v soft</li> <li>hard v soft</li> <li>hard v soft</li> </ul>                      | FIFO            | )1024<br>)1024<br>]1024<br>]1024          |

| Thread n.1<br>Thread n.1<br>Thread n.4<br>Thread n.5<br>Thread n.6 | Command<br>tion<br>Assigned core  | ji<br>ji<br>ji      | <ul> <li>hard v soft</li> </ul> | FIFO            | Ĭ1024<br>Ĭ1024<br>Ĭ1024<br>Ĭ1024          |

| Thread n.1<br>Thread n.1<br>Thread n.4<br>Thread n.5<br>Thread n.6 | Command<br>tion<br>Assigned core  | ji<br>ji<br>ji      | <ul> <li>hard v soft</li> </ul> | FIFO            | j1024<br>j1024<br>j1024<br>j1024<br>j1024 |

| Thread n.1<br>Thread n.1<br>Thread n.4<br>Thread n.5<br>Thread n.6 | Command<br>tion<br>Assigned core  | ji<br>ji<br>ji      | <ul> <li>hard v soft</li> </ul> | FIFO            | Ĭ1024<br>Ĭ1024<br>Ĭ1024<br>Ĭ1024          |

You can assign to each thread a core.

| 🥺 Core management                                                                |             |

|----------------------------------------------------------------------------------|-------------|

| Thread and core management of the PC platform for Rapid Control Prototyping (RCF | <b>')</b> : |

| J default PC platform core management                                            |             |

| 📧 custom PC platform core management: Number of core of the PC: 4                |             |

|                                                                                  |             |

|                                                                                  |             |

| Ok ?                                                                             | Cancel      |

#### You can configure the threads:

- the assigned core, (in case of 'custom core management')

- the priority,

- the hard real time execution capability,

- (hard or soft),

- the schedule policy, (FIFO or Round Robin),

- the stack dimension.

excellence and passion in automatic control design The scheduling in the Rapid Control Prototyping phase

# The scheduling window and the Scheduling constraints

The control functions are listed thread by thread.

All the Control functions belonging to a same thread must have the same period,

two Control functions belonging to a same thread must not be overlapped,

Each asynchronous

Processor Input

has its specific thread.

EICASLAB supports you and prevents you to make scheduling errors.

excellence and passion in automatic control design

he Professional Software Suite for Automatic Control Design and Forecasting